03-Combinational_Logic_Design

I Verilog HDL

I.1 Introduction

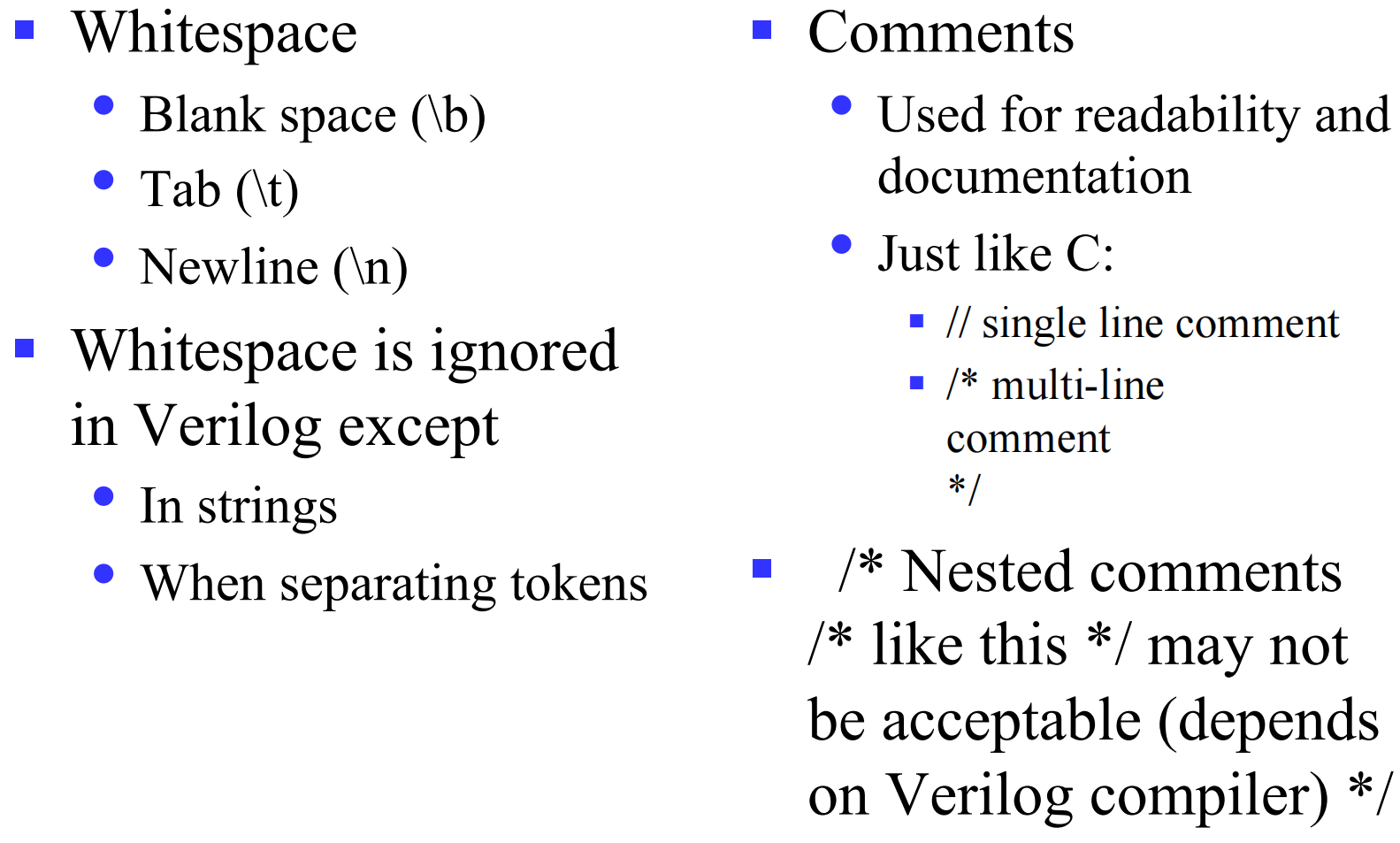

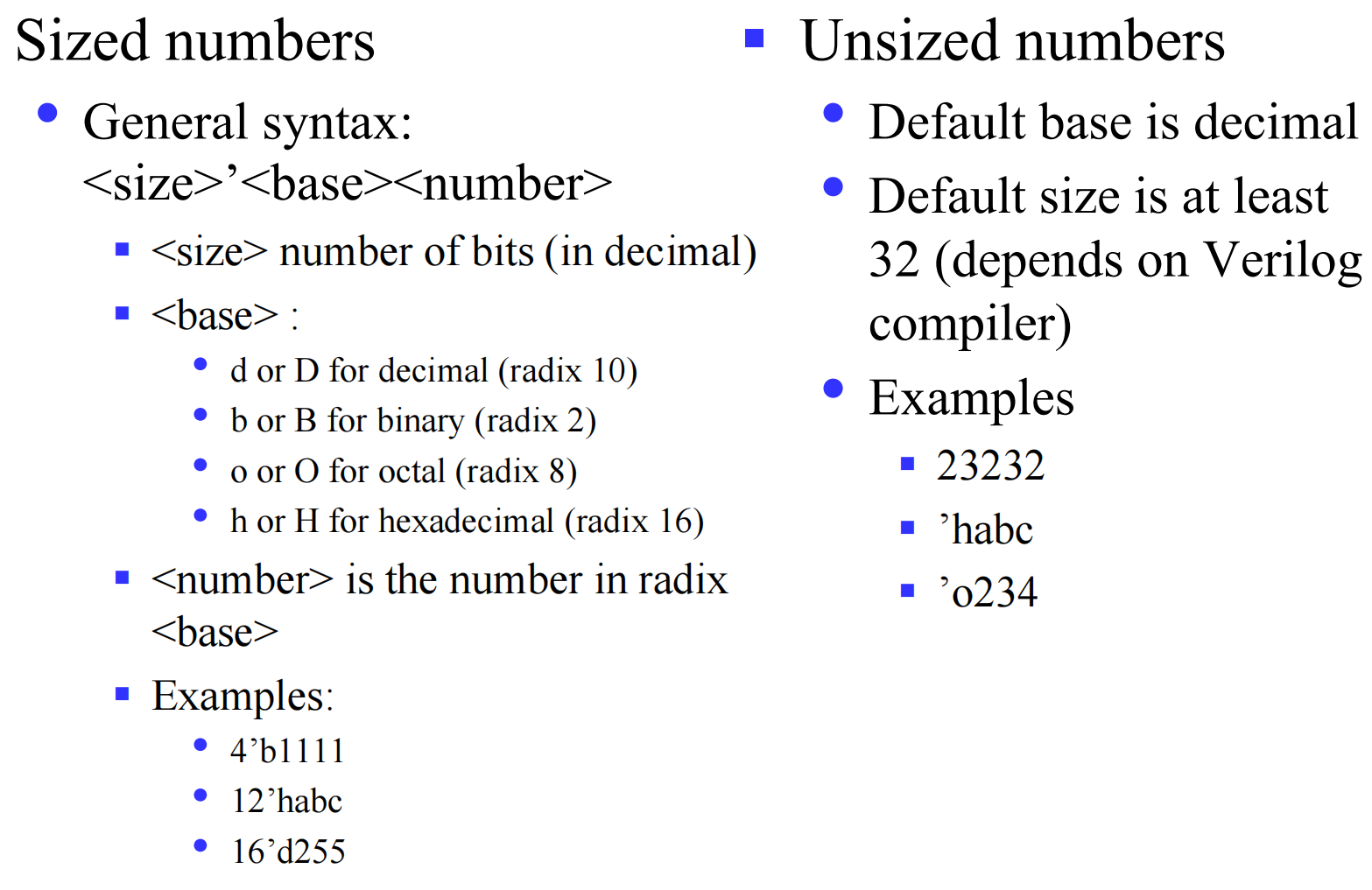

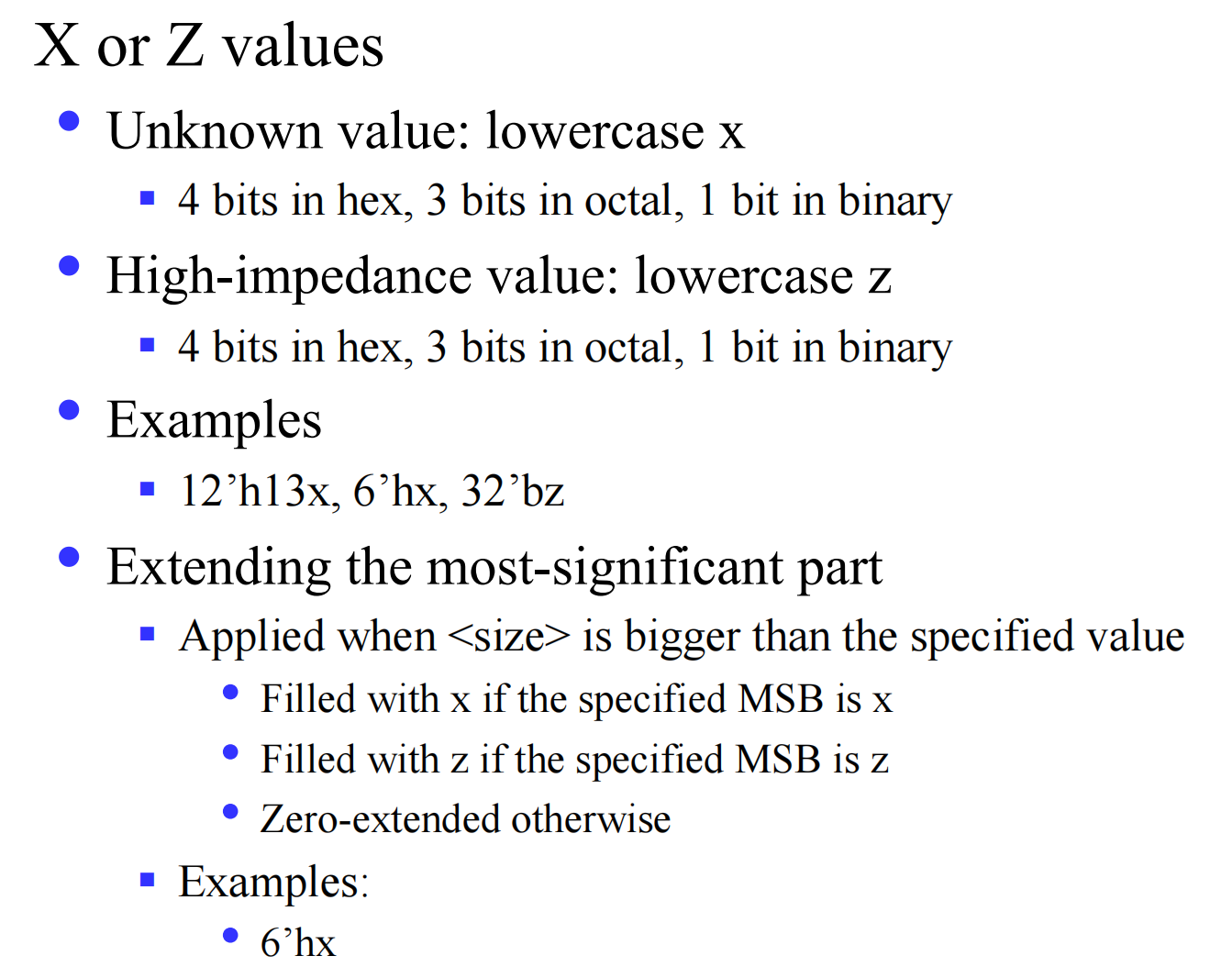

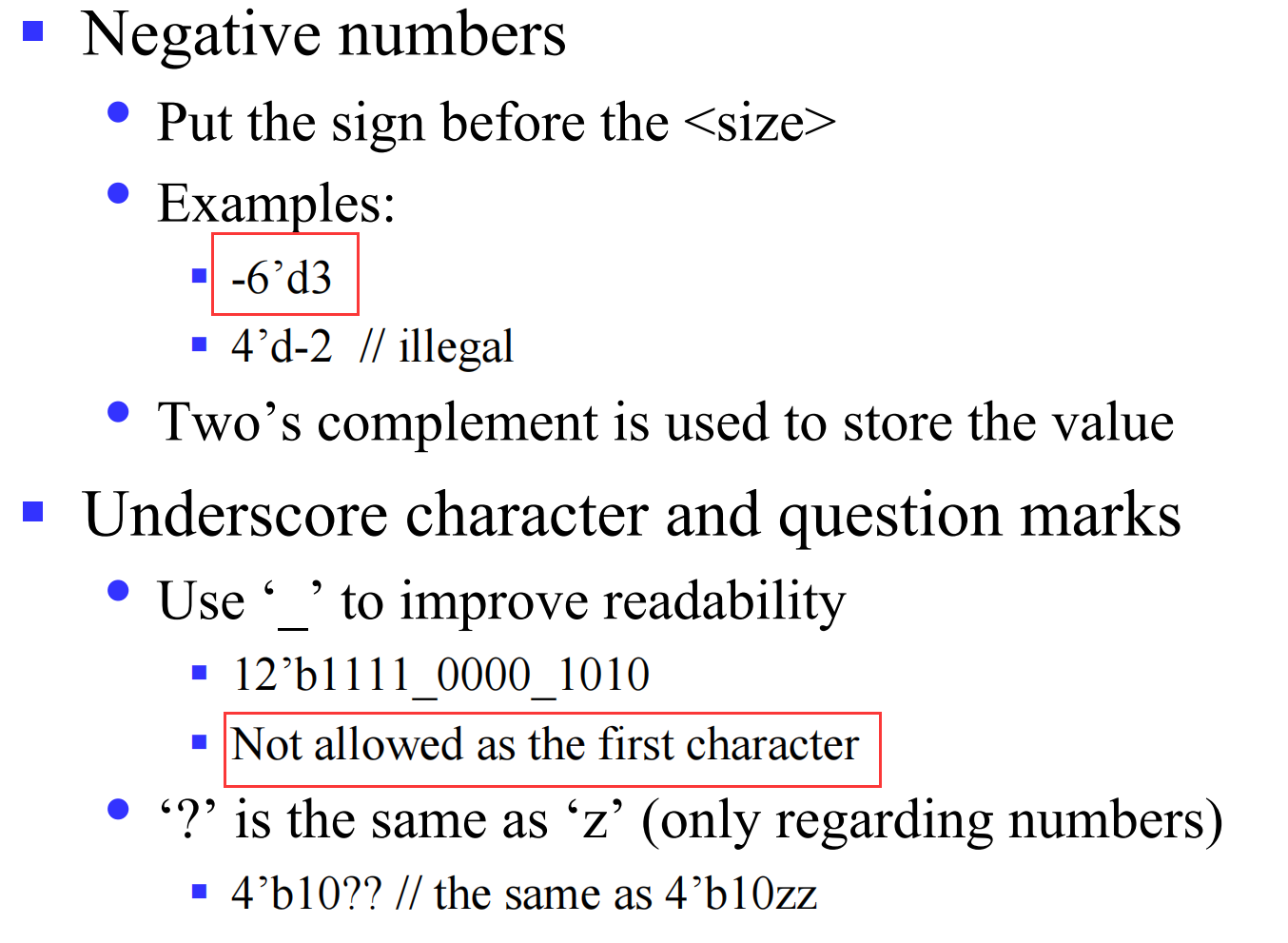

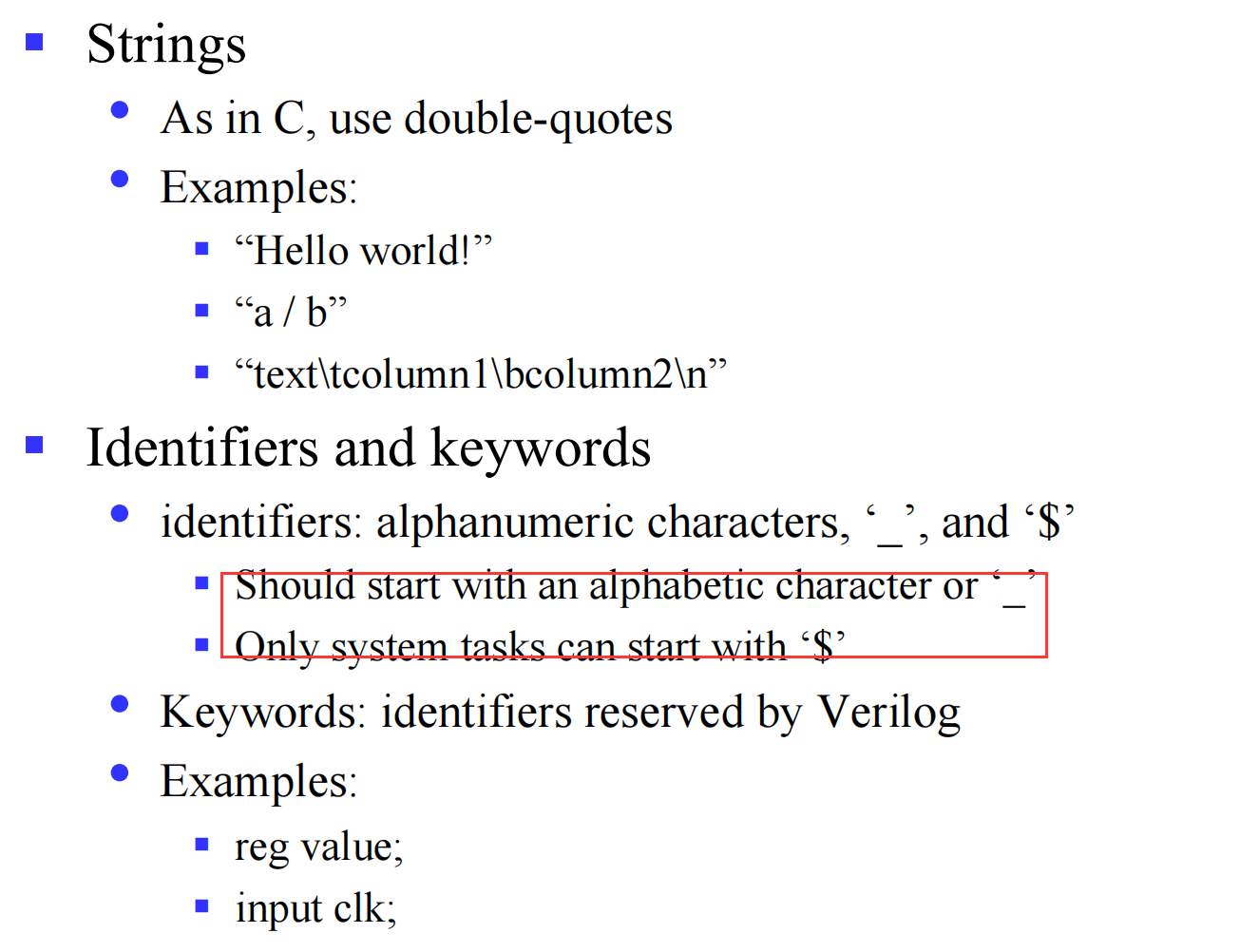

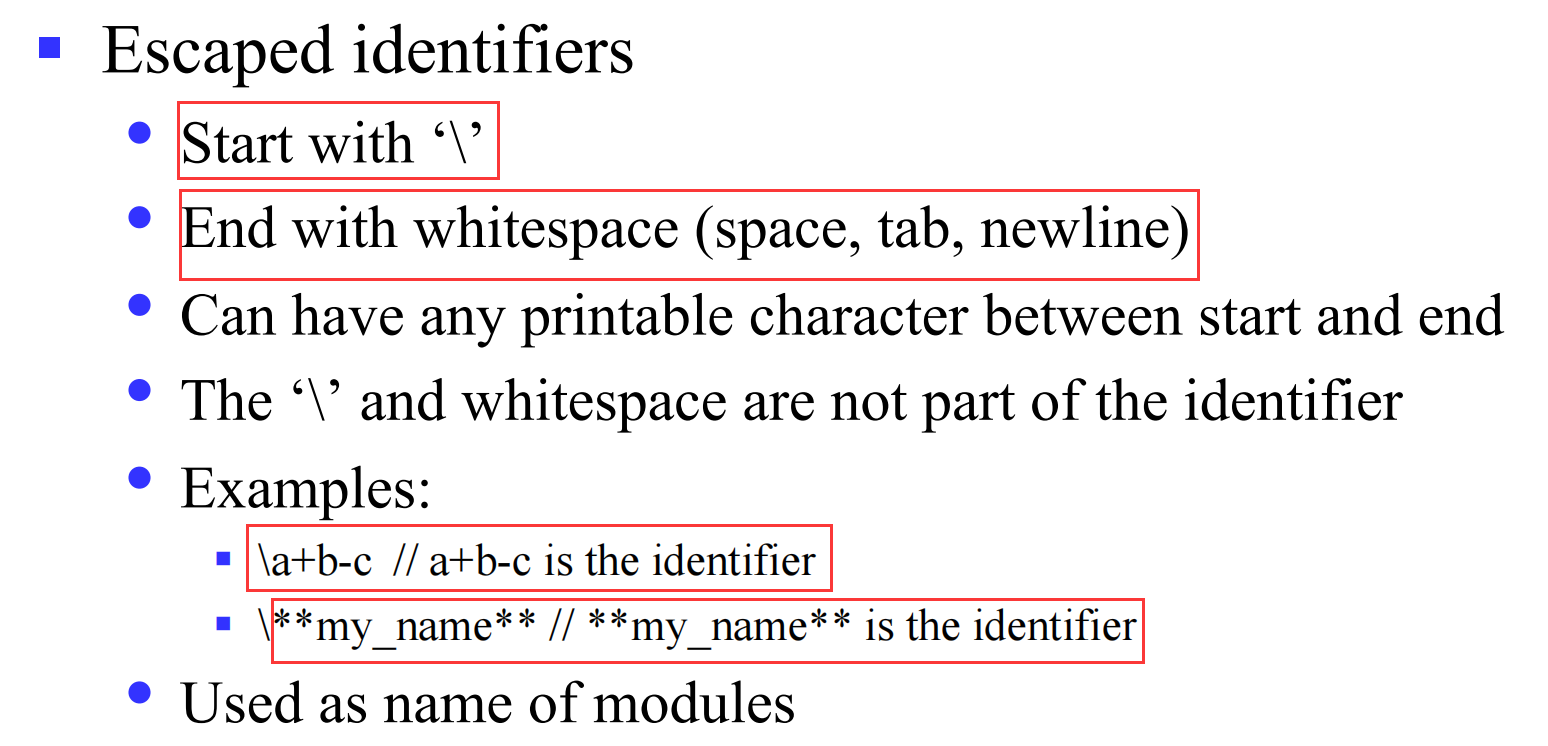

I.1.1 Lexical Conventions(词汇约定)

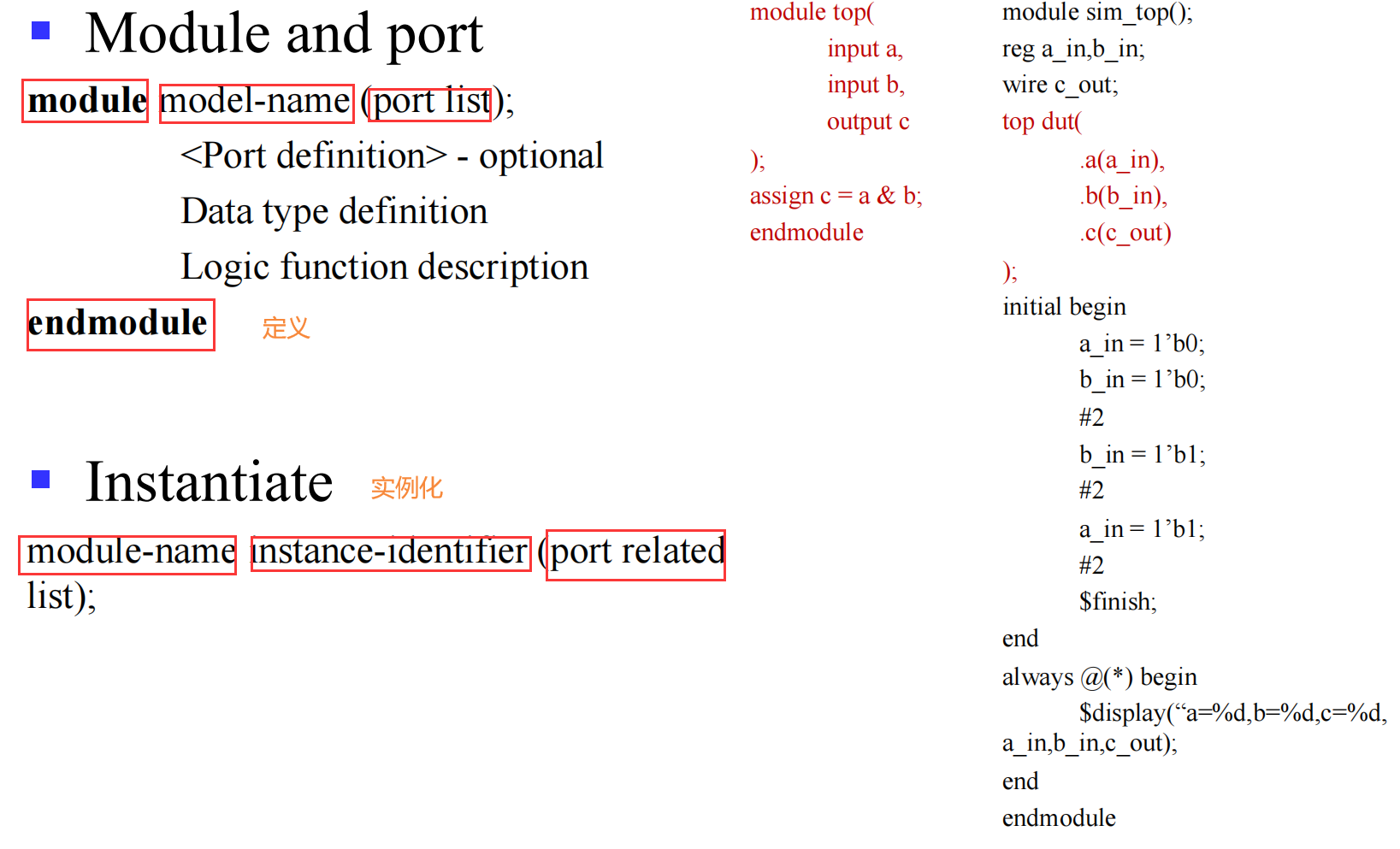

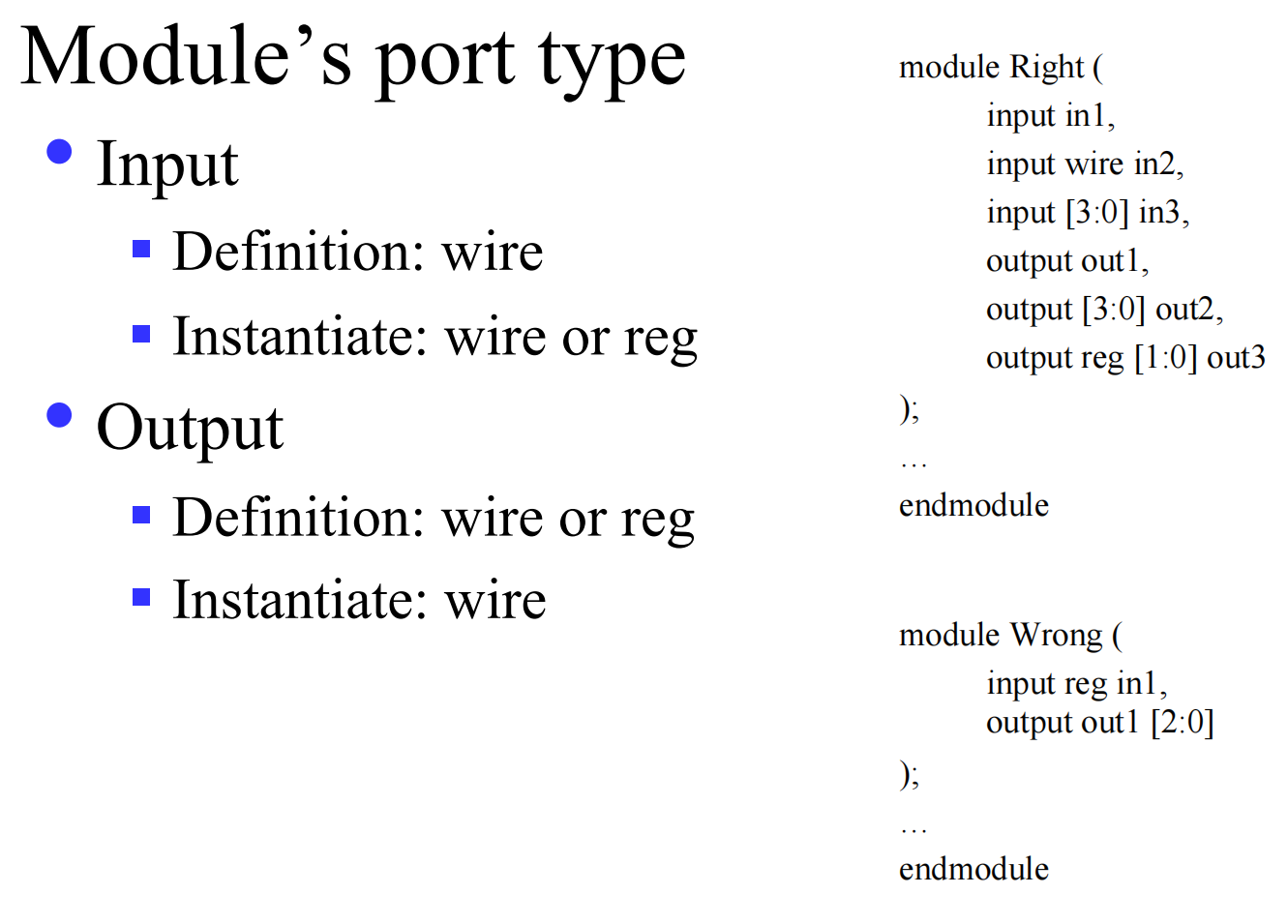

I.1.2 Basic Syntax: Module, Port and Instantiate

Attention

当实例化的模块含参数时,参数列表应该写在 instance-identifier 前面

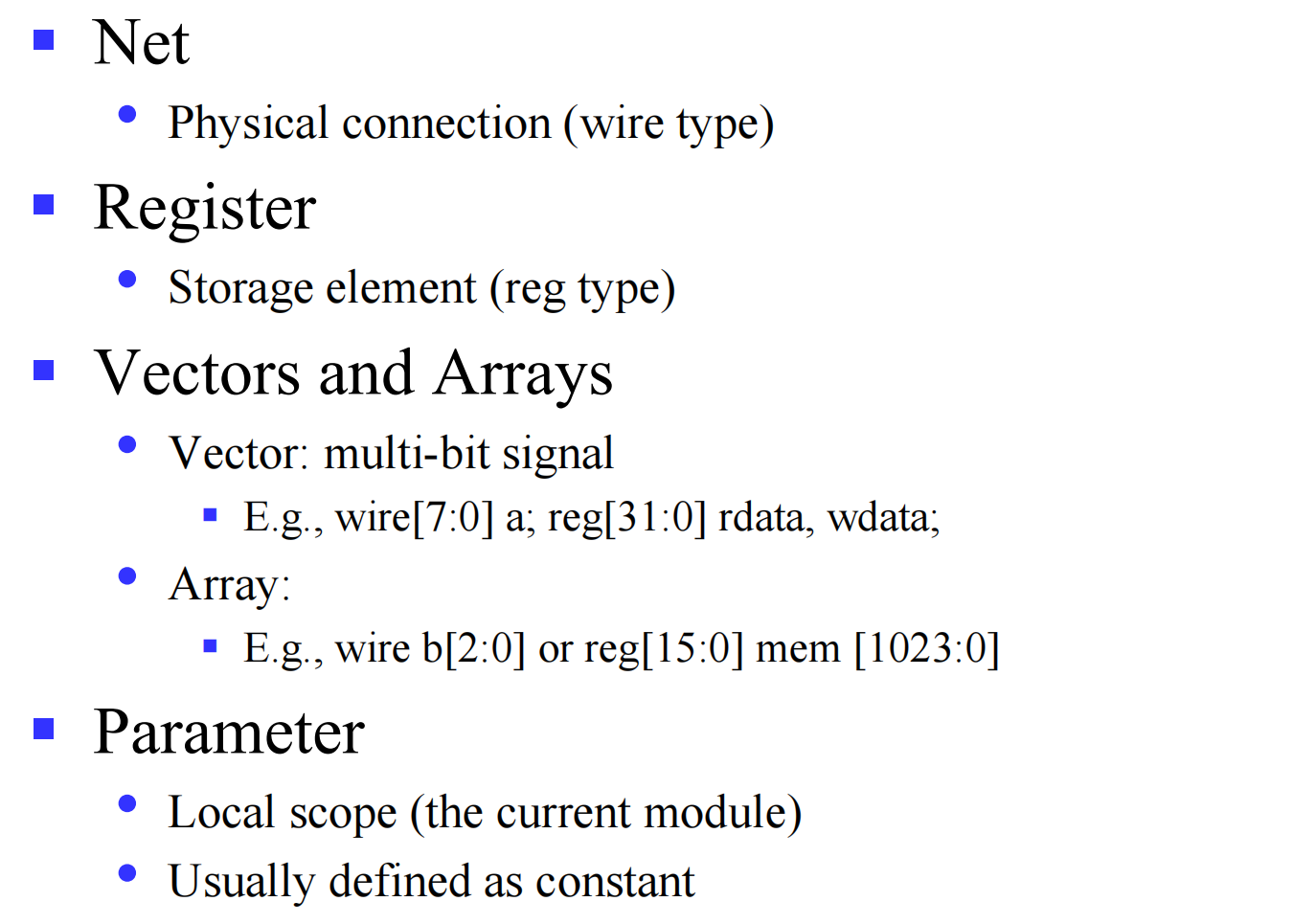

I.1.3 Basic Syntax: Data Type

I.2 Modeling methods

I.2.1 Structured modeling

• Module-level

根据逐层调用自己构建的模块来完成复杂的工程,就像我们在 C 语言中使用函数一样

• Gate-level

通过调用门级电路来完成

• Switch-level

通过调用硬件内部的晶体管

I.2.2 Dataflow modeling

• Suitable for modeling combinational logic circuits

• Use continuous assignment statements: assign

I.2.3 Behavioral modeling

always @(event signal list) procedure statement

I.3 testbench

lab 里面经常会用的,作为仿真的测试输入。

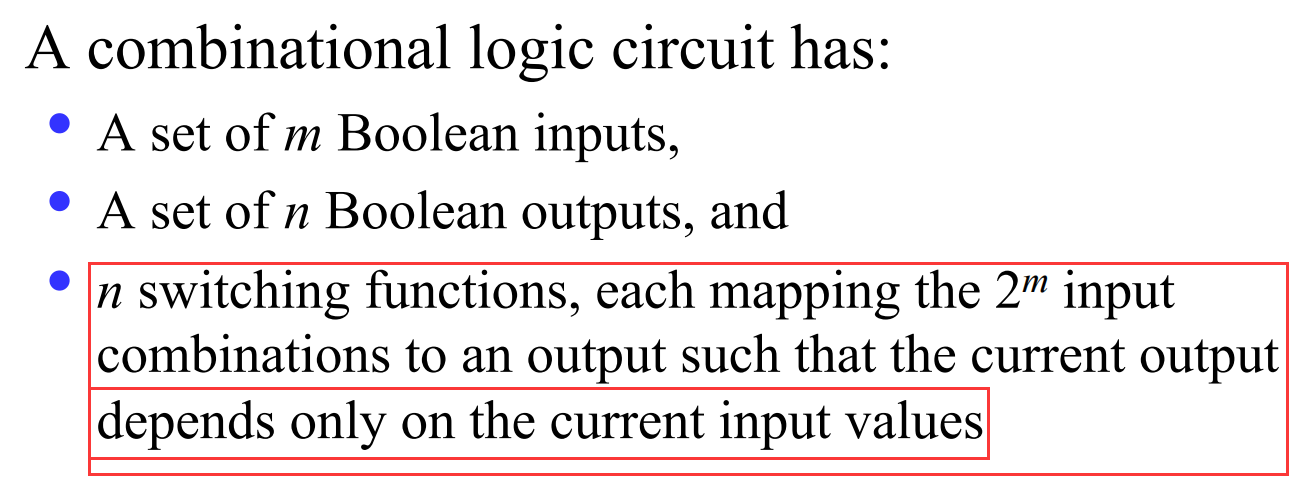

II Combinational Logic Circuit

II.1 2-level vs. multi-level

| speed | cost | |

|---|---|---|

| two | fast | high |

| multi | low | low |

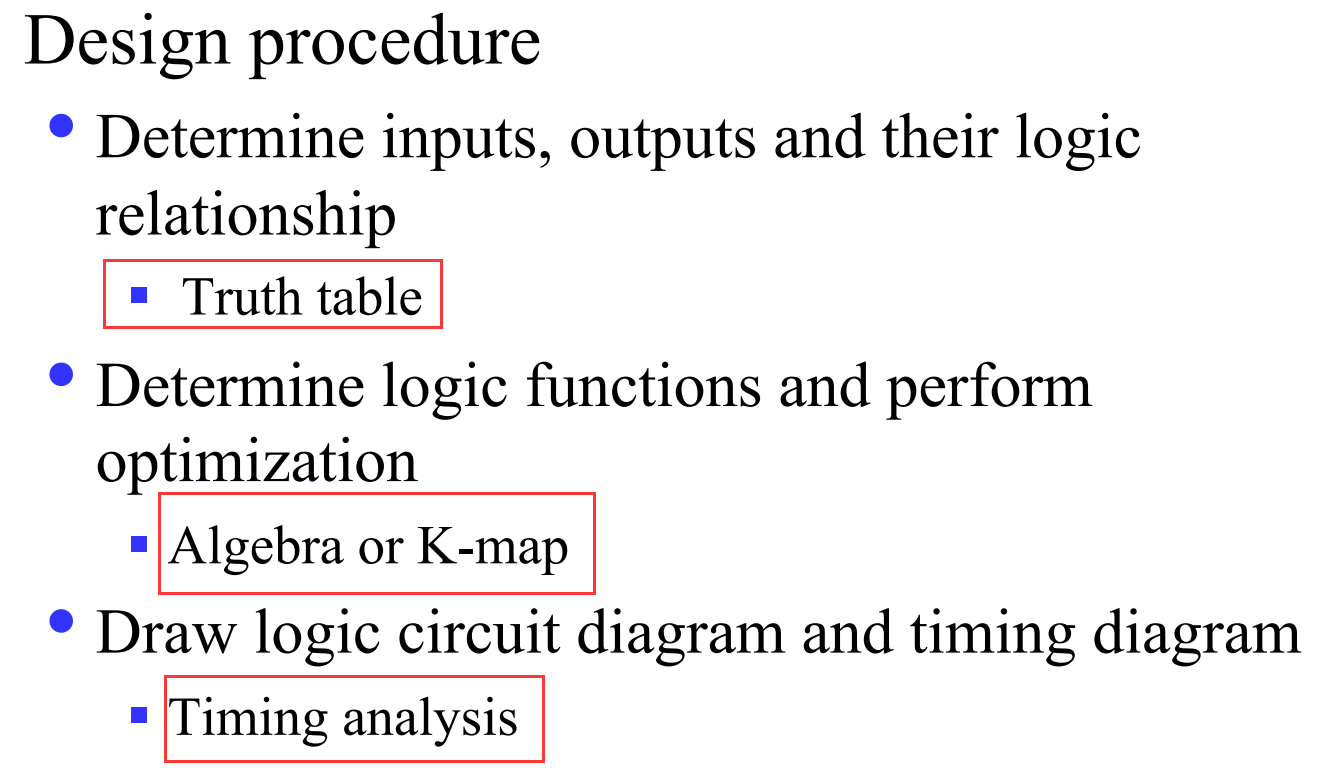

II.2 design

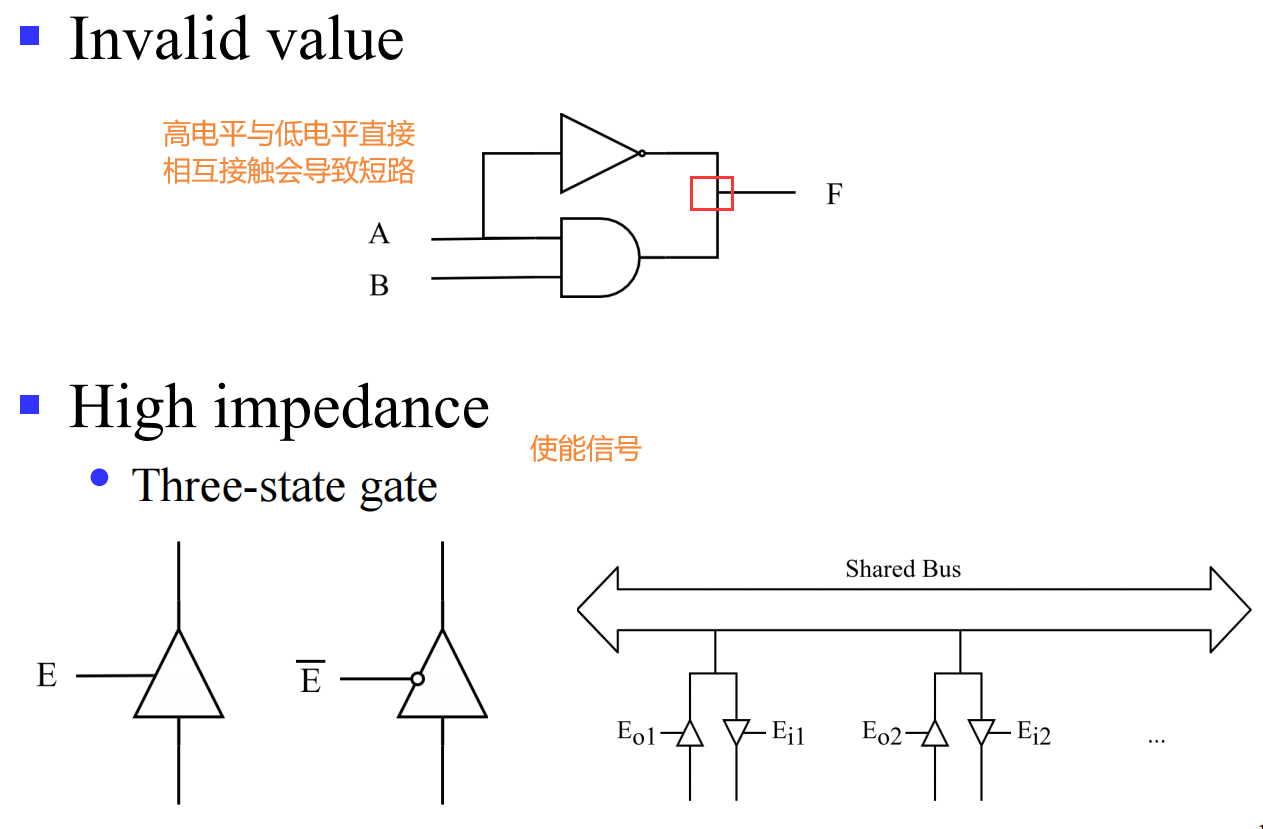

II.3 special value

III Some Classic/Basic Designs

下面大多在 lab 中会实现

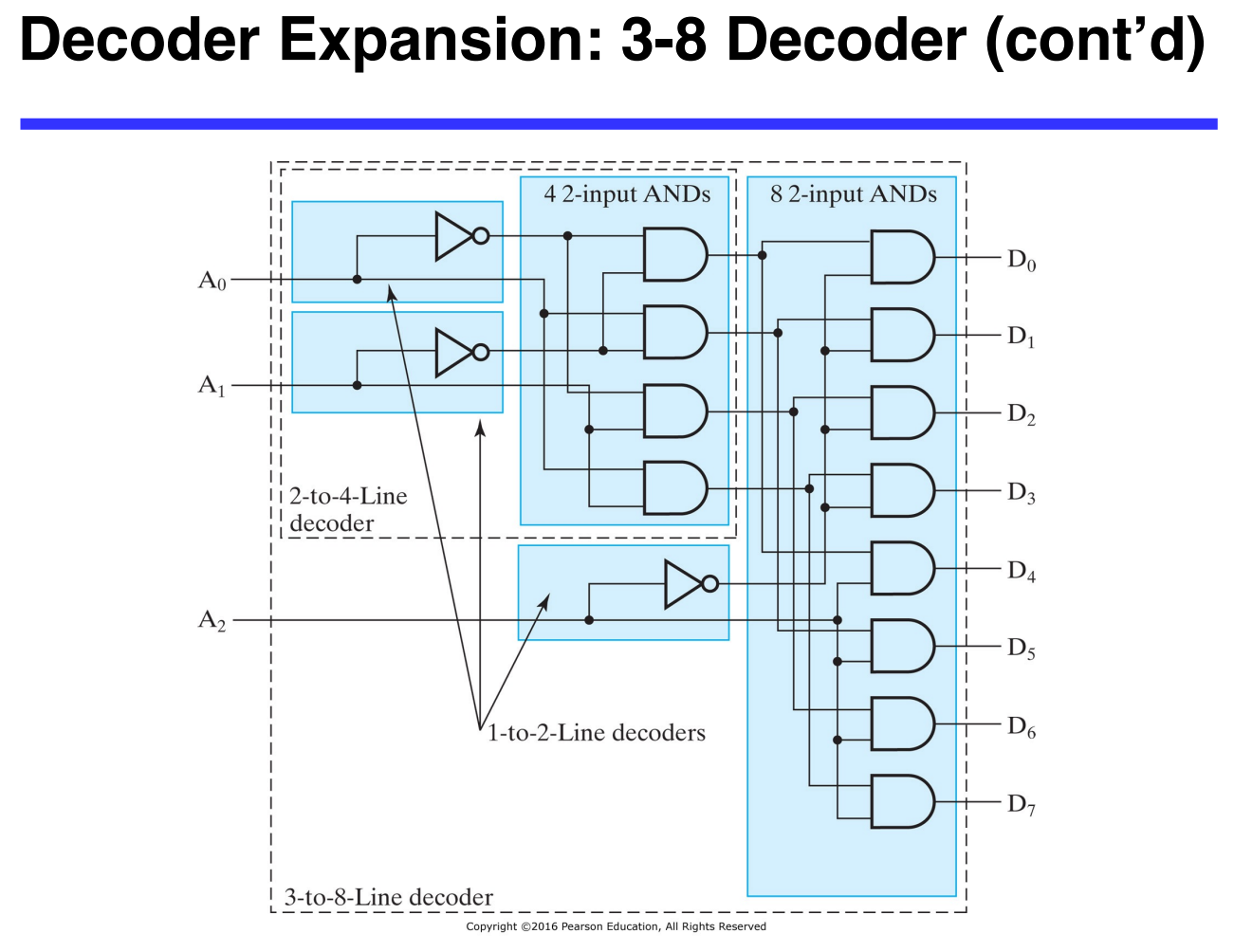

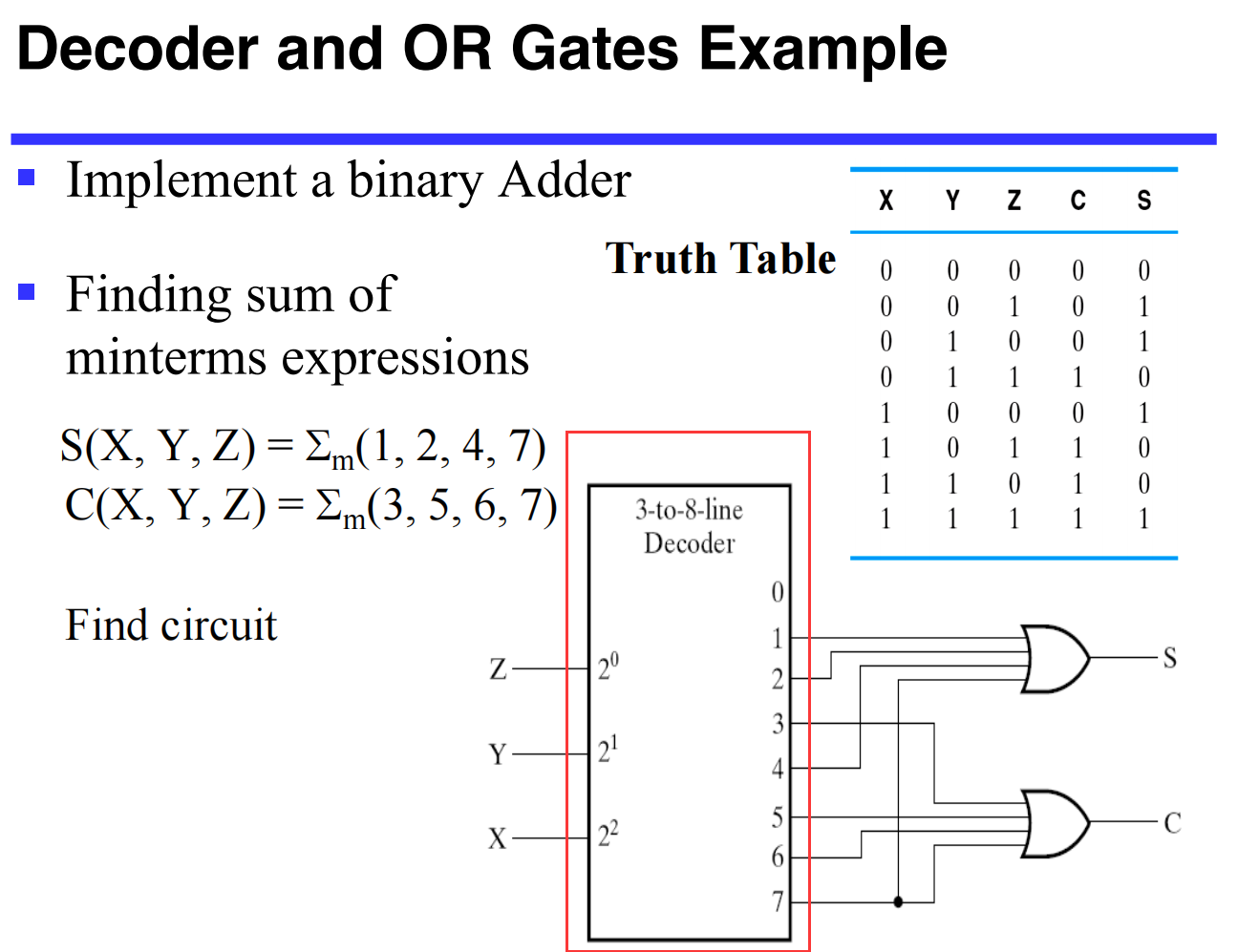

III.1 Decoder

实验指导中的一/独热码 one-hot code,实现如下

可以用于实现组合逻辑电路

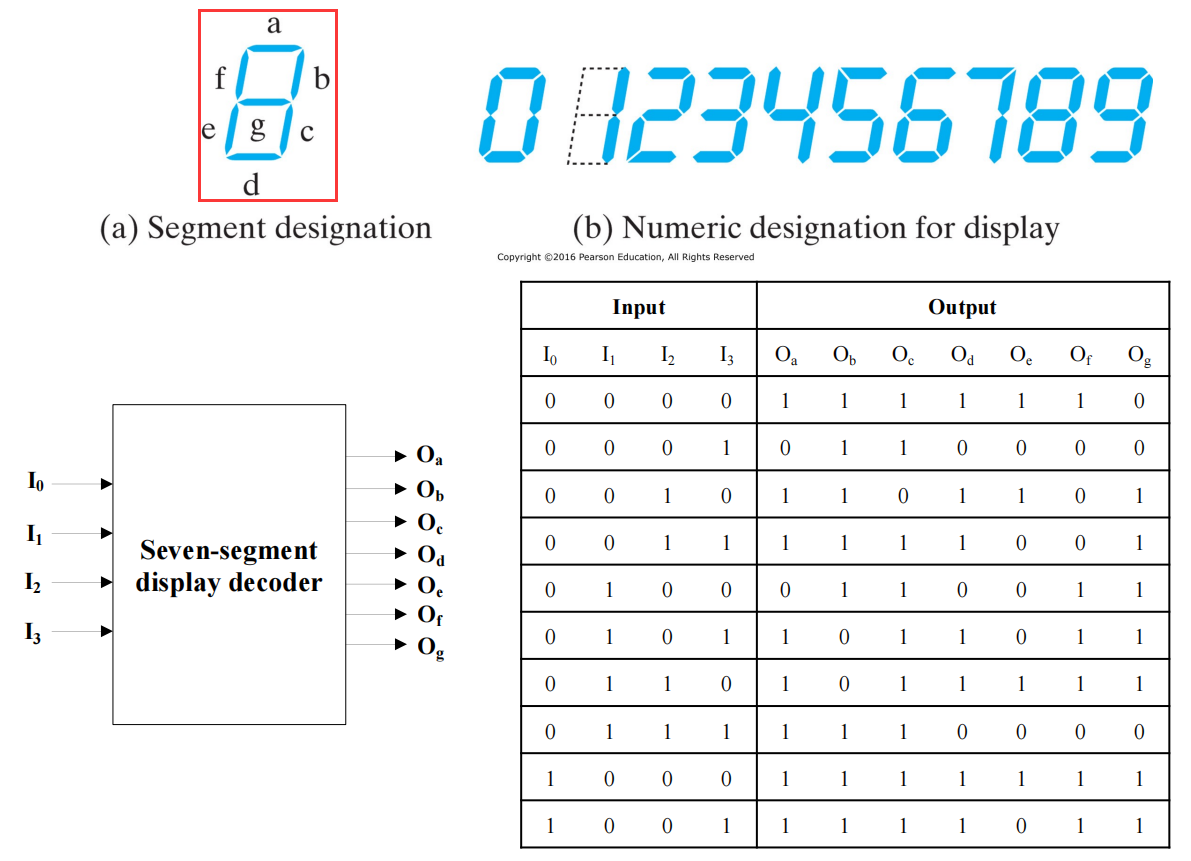

III.2 Seven-Segment Display Decoder

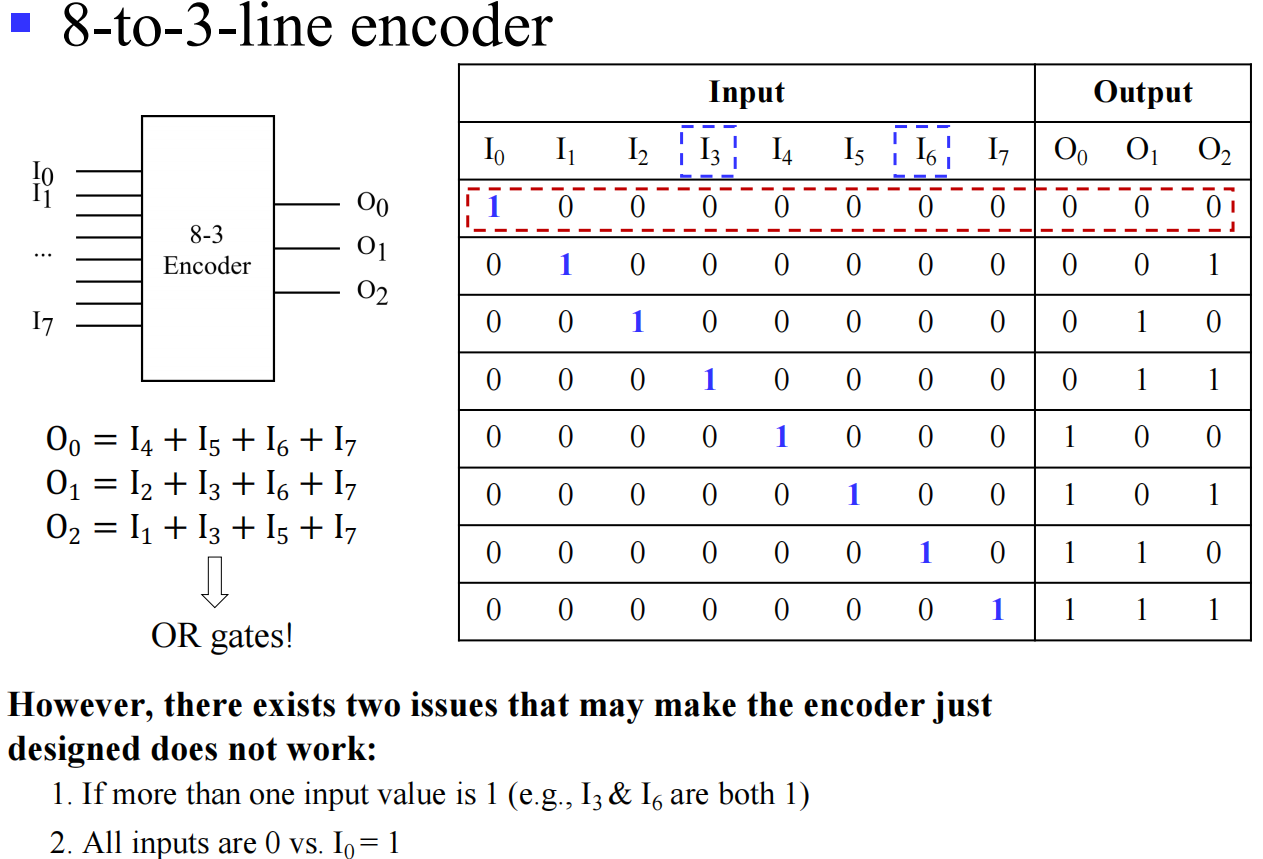

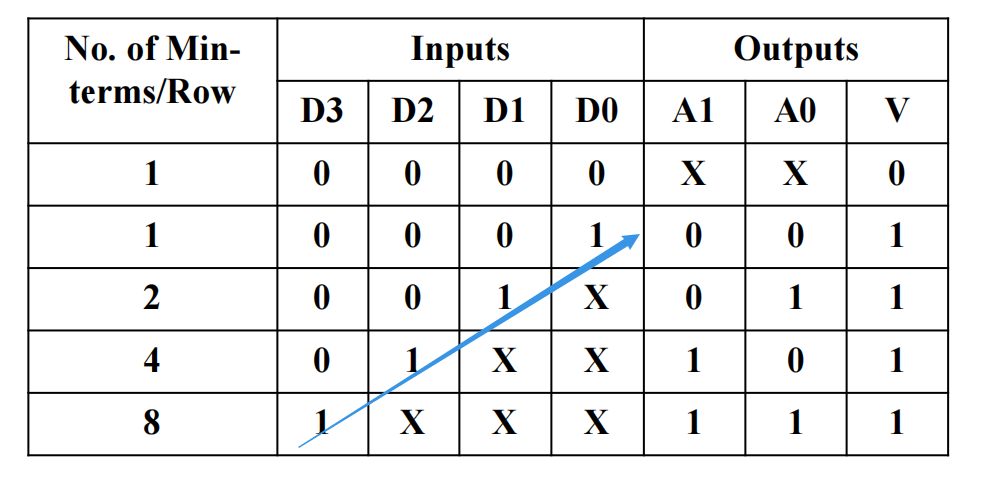

III.3 Encoder

考虑到一些不正常的输入(比如全为 0 或者多个 1),引入了 Priority Encoder

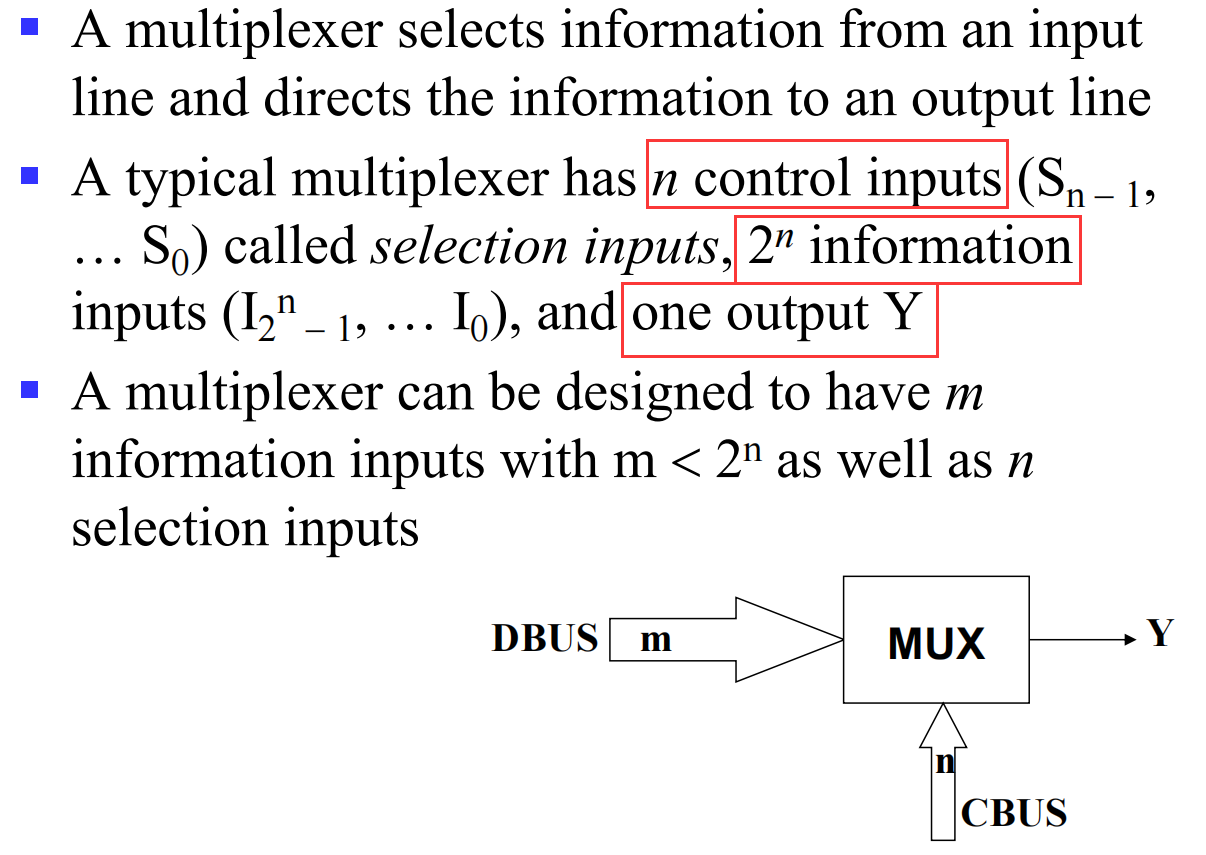

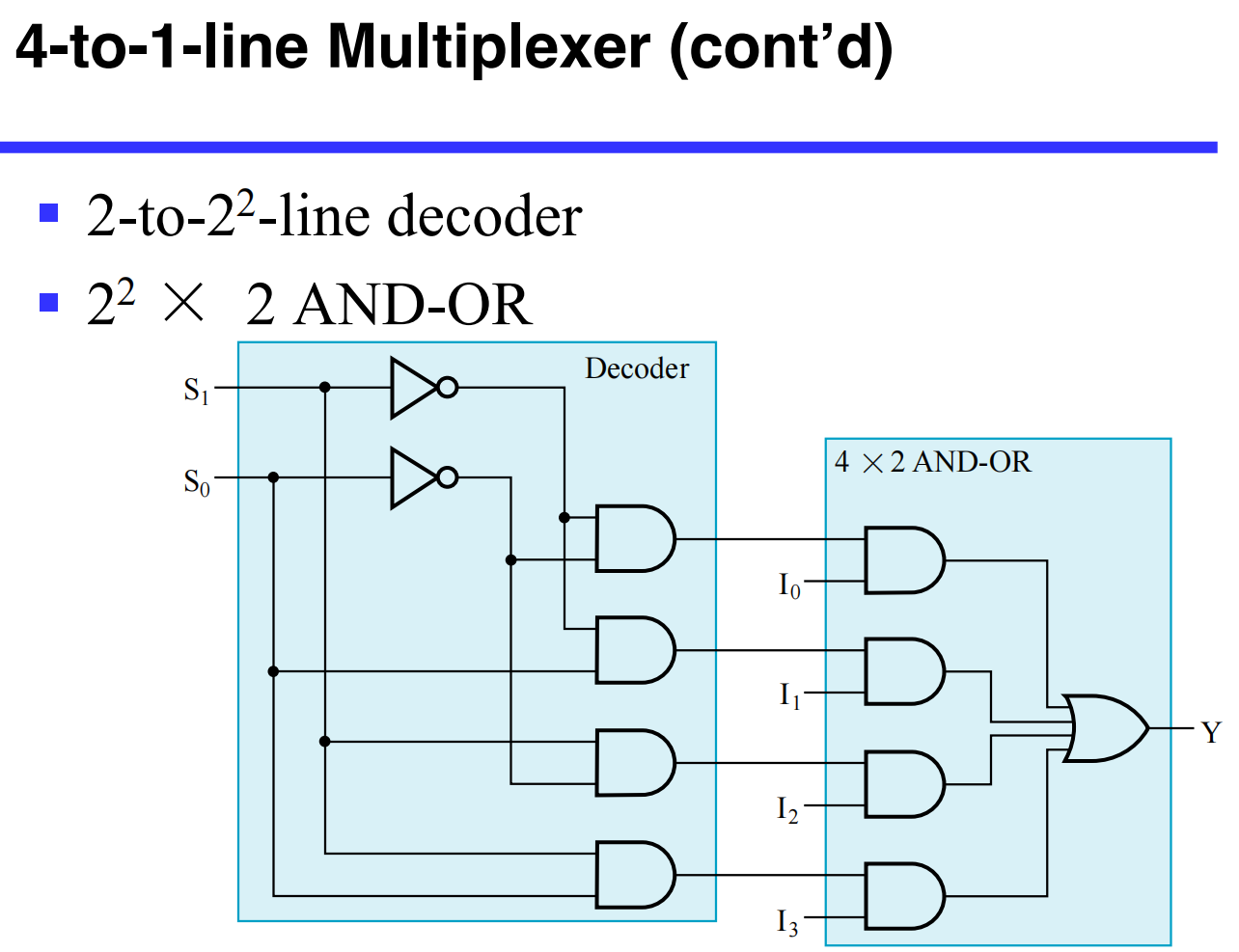

III.4 Multiplexer

III.4.1 example

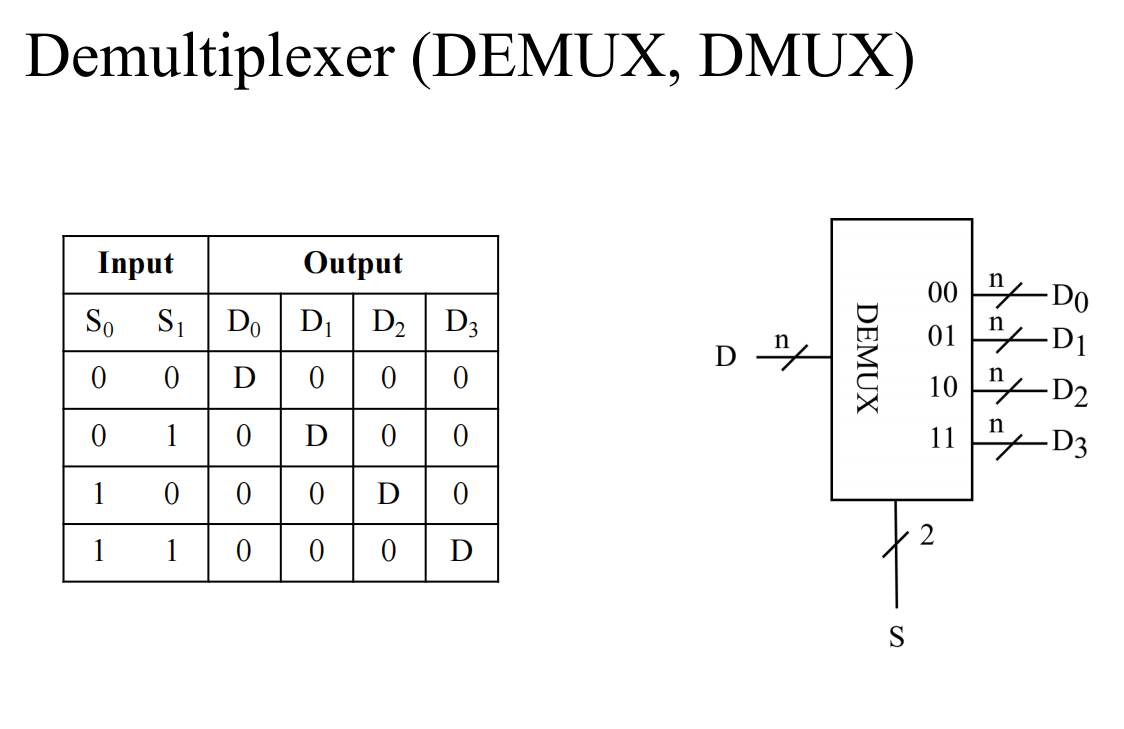

III.5 Demultiplexer

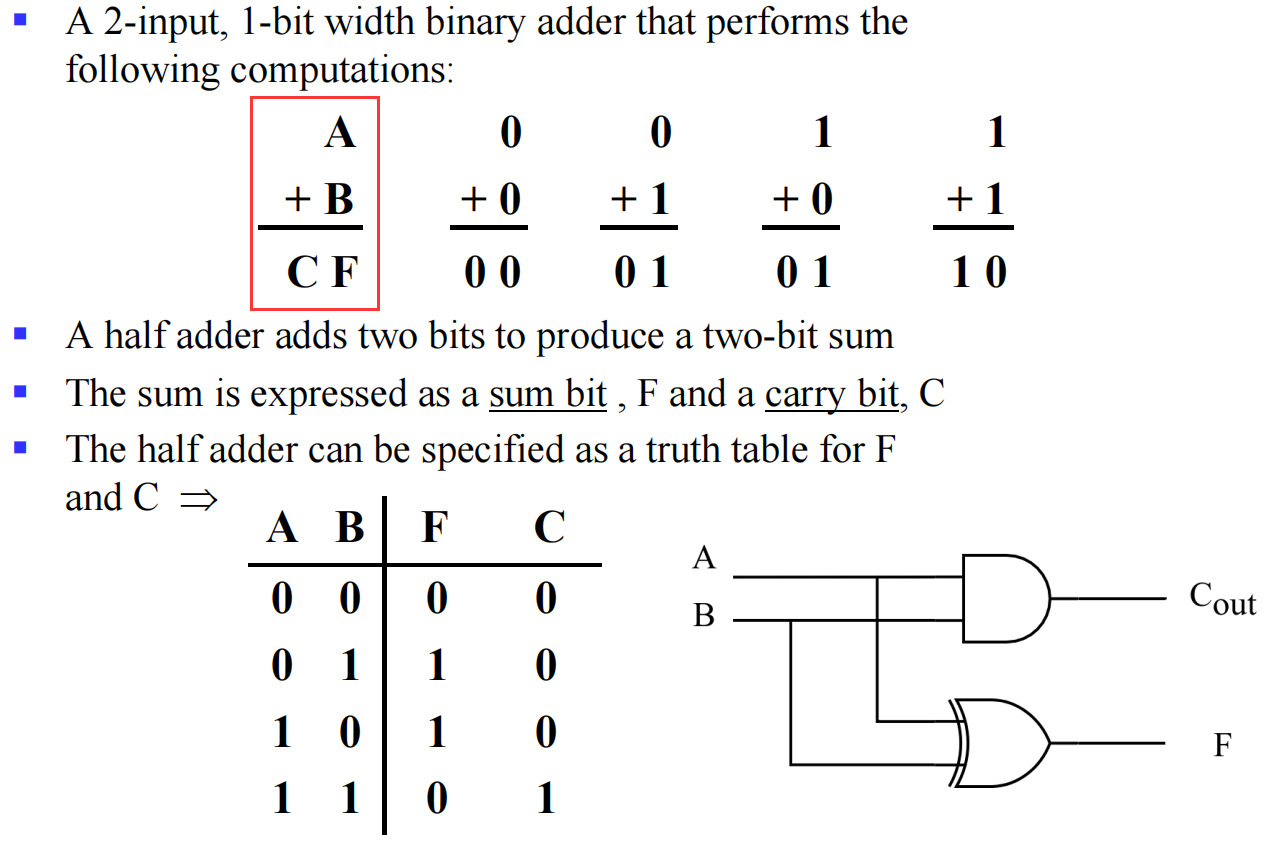

III.6 Half-Adder

实现最基本的加法,输出结果和进位

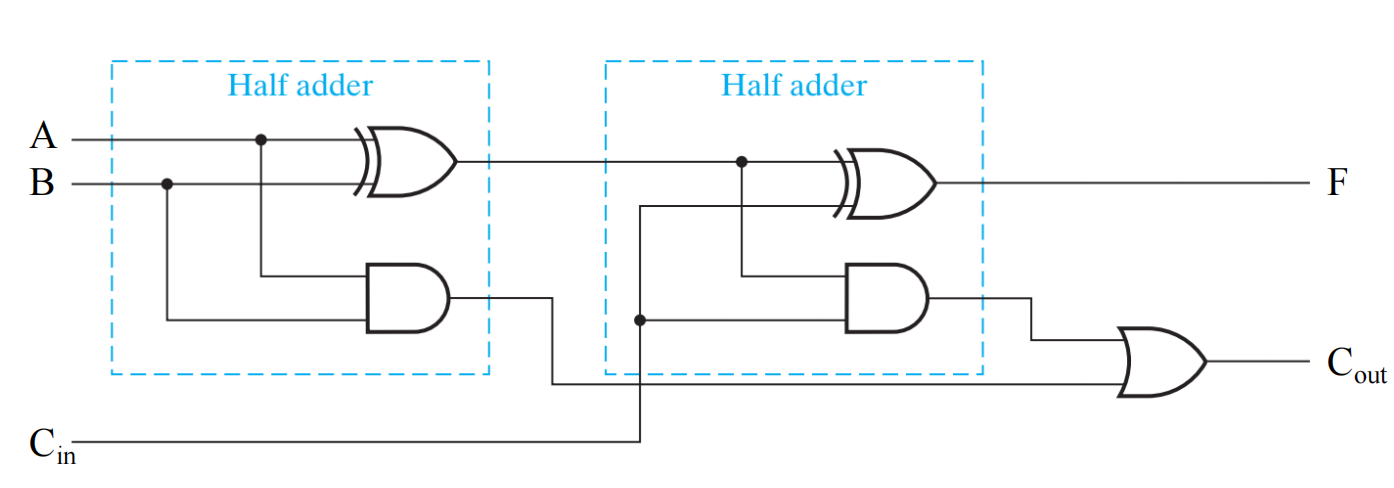

III.7 Full adder

III.7.1 simple full adder

用两个半加器将三者加起来

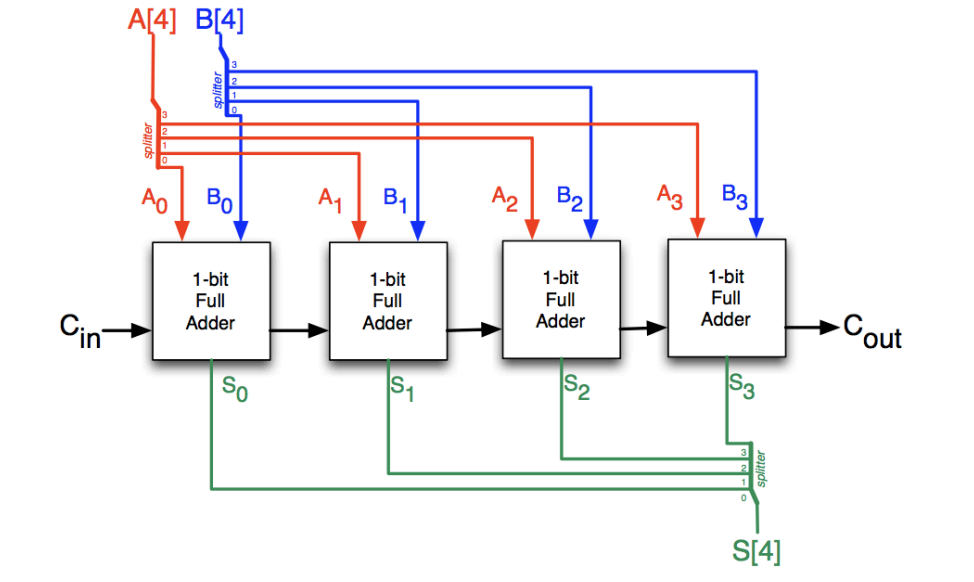

III.7.2 ripple-carry adder(行波进位加法器)

将低位的进位 Cout 输入给高位一起加,这和我们手动加法是一致的

III.7.3 carry-lookahead adder(超前进位加法器)

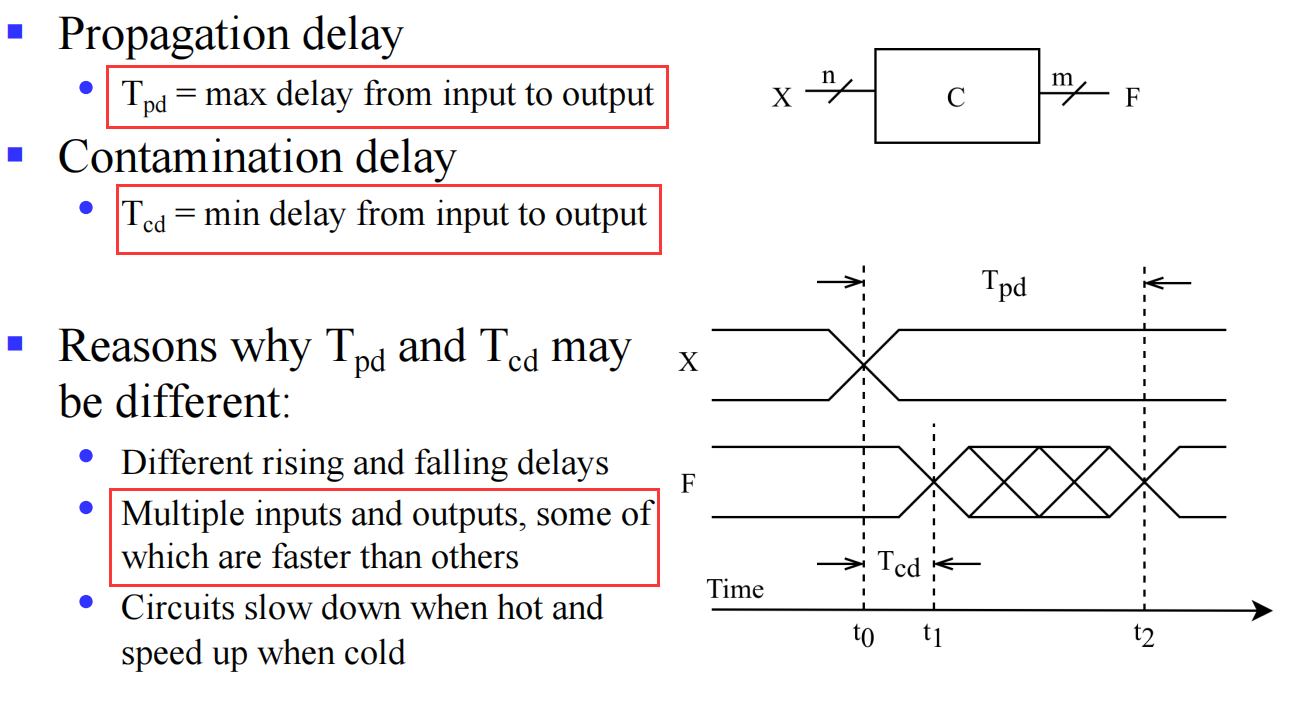

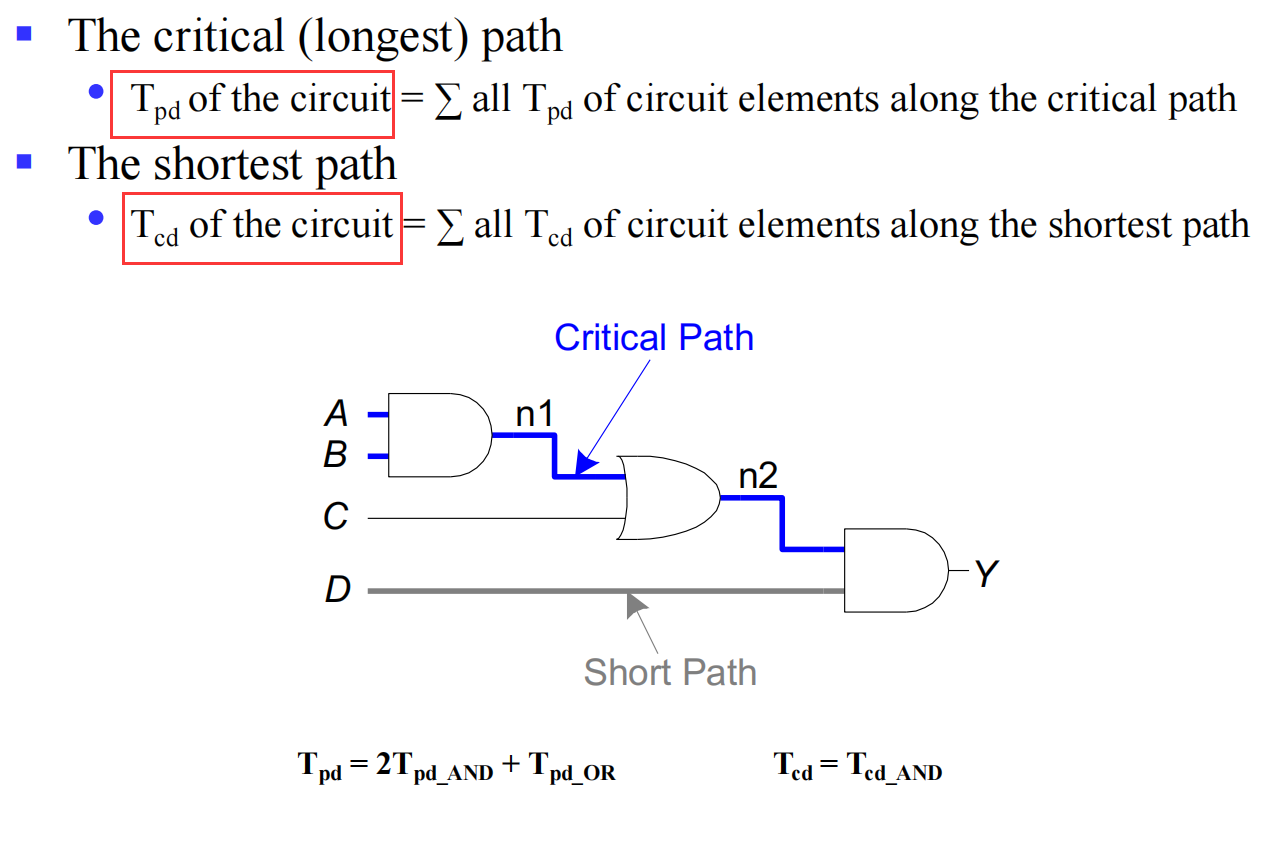

IV Timing Analysis

有向无环赋权图 [Activity On Vertex Network (AOV 网)](../../DMPT/notes/05-Graph-Theory.md #Activity -On-Vertex-Network-(AOV-网))

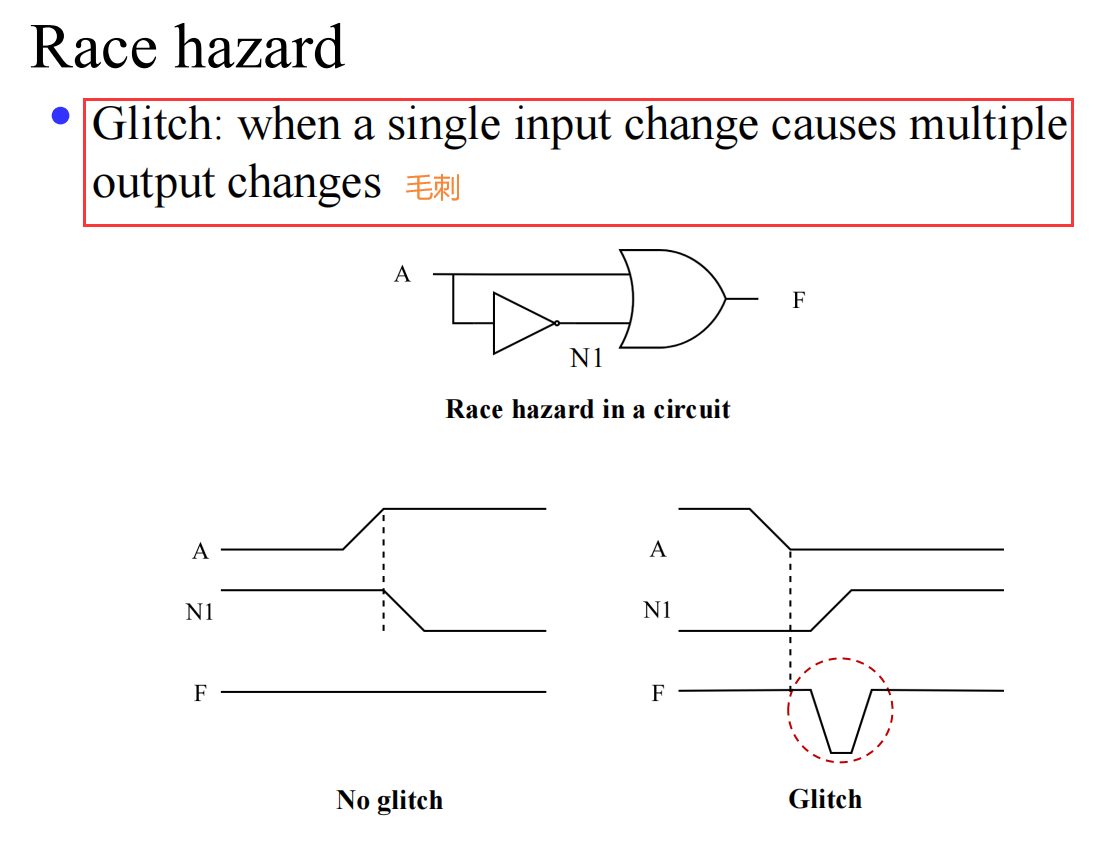

一个可能都应对方法:在没有非门的路上加延迟电路以便二者信号同时进入与门